Overview

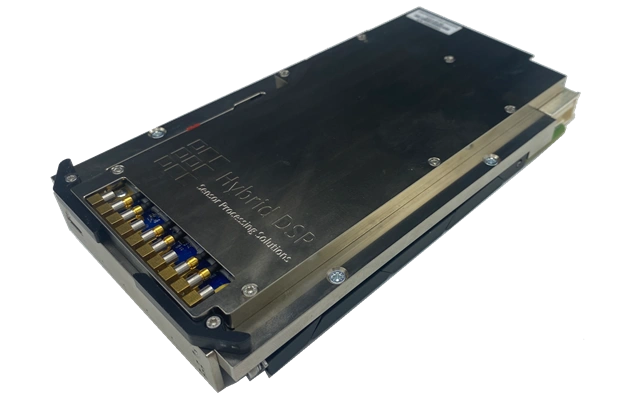

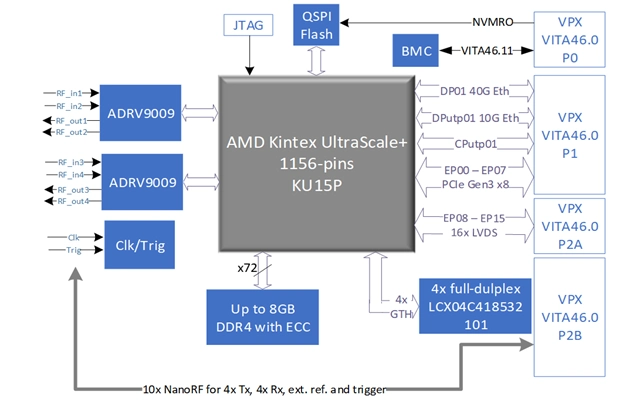

The 3U VPX V3UFR102P7 modular RF transceiver is a member of Hybrid DSP’s XU01P 1156 Core Series of mid-range, cost effective, rugged processing boards based on the AMD Kintex UltraScale+TM A1156 FPGA package, up to 8GB DDR4 and an ARM-based Board Management Controller (BMC).

The V3UFR102P7 offers four phase-coherent channels with an RF coverage of 1 MHz to 6 GHz makes the board ideally suited for EW and radar applications.

The V3UFR102P7 is available with a range of build options for OpenVPX air and conduction cooled based systems as well as those aligned with the SOSA Technical Standard. The default build is a conduction-cooled SOSA aligned version with 4x10Gbps optical (Ethernet) interface to the backplane, combined with 4 Rx, 4 Tx, Clock and Trigger connecting to the VITA67.3D connector using NanoRF coax.

Main features

- 3U VPX FPGA Carrier with integrated RF transceiver

- AMD® UltraScale+™ KU15P FPGA processor

- Four Rx Channels, 200MHz BW, 16-bit ADC resolution

- Or dual channel Rx in observation mode, 450MHz BW

- Four Tx Channels, 450MHz BW, 14-bit DAC resolution

- Tuning range from 75MHz to 6GHz

- Bandpass RF filters on each receiver

- SOSA Aligned

- Profile: SLT3-PAY-1F1U1S1S1U1U4F1J-14.6.13-4

- LightCONEX® 4TRX Optical Module on-board

- 10 NanoRF to VITA67.3D connector

- Data & expansion planes for high-speed protocols

- Up to 8GB DDR4 ECC memory

- Air or conduction cooled

Technical specifications

Main Processor and Memory

- AMD Kintex UltraScale+TM A1156 FPGA XCKU15P

- DDR4 4GB or 8GB with ECC

Board Management

- Voltage and temperature monitor

- Power/reset control

- Tier-3 VITA 46.11 IPMI

Backplane Architecture (3U)

- Up to 16 serial transceiver lanes on VPX P1 (PCIe Gen3, Aurora, Ethernet, RapidIO etc)

- 16 LVDS on VPX P2A (can be disconnected)

- 4 TRX 10.3125Gbps optics on VPX P2B supporting 10Gb Ethernet

- 10 NanoRF to FMC on VPX P2B

Front/Rear I/O

- 4 Rx Channels, 450MHz BW, 16-bit ADC resolution

- 4 Tx Channels, 450MHz BW, 14-bit DAC resolution

- External Reference

- External Trigger

Mechanical

- 3U VPX COTS air- and conduction-cooled

- OpenVPX and VPX-REDI

- Pitch: 1”

Board Support Package

- Vivado project, VHDL based reference designs, UART and PCIe drivers, API, Python and C/C++ sample applications

Compliance

- OpenVPX System Specification encompasses VITA 46.0, 46.3, 46.4, 46.6, 46.7, 46.9, 46.11

- Compatible with VITA 65 and SOSA aligned systems

- VITA 47.0

- VITA 48.0/48.1/48.2 (REDI)

VITA 47.0 Construction, Safety and Quality

- Environmental Class: EAC1, EAC6, ECC1 and ECC3 (-40°C to +70°C operating temperature range)

- IPC-A-610D Class 3 and IPC-A-600G Class 3

- Conformal Coating: IPC-CC-830B